SEICSE International Journal of Computer Sciences and Engineering Open Access

E-ISSN: 2347-2693

# Design and Verification of Serial Peripheral Interface Master Core Using Universal Verification Methodology

# Punith Kumar M B<sup>1\*</sup>, Sreekantesha H N <sup>2</sup>

<sup>1,2</sup>Department of ECE, PESCE, Mandya, India

Corresponding Author: punithpes@gmail.com

DOI: https://doi.org/10.26438/ijcse/v7si14.711 | Available online at: www.ijcseonline.org

*Abstract-*-In today's world, number of communication protocols for both long and short distance communication purpose, long distance protocols is USB (Universal Serial Bus), ETHERNET, PCI-EXPRESS. SPI (Serial Peripheral interface) and I2C are used for short distance communication protocols. SPI is one of the commonly used bus protocol for connecting peripheral devices to microprocessor .SPI is full duplex, high speed an synchronous bus protocol used for on-board or intra-chip communication In this project the configurable architecture of SPI Protocol with Wishbone Interface has been designed .The main advantage of this design is it overcomes the weaknesses of traditional SPI Bus protocol. As the complexity of the circuit is numerous so there is need of verification methodology to quench the product failure. This project emphasizes on verification of SPI master core verification using Universal Verification Methodology.

Keywords—SPI, Wishbone, UVM, SystemVerilog.

### I. INTRODUCTION

The development of advanced integrated circuits not only increased the complexity of IC design but also IC verification equally challenging. Around 70% spend on verification and verification is a critical path and time can be reduced through automation [1]. many protocols used for both long and short distance communication purpose, long distance protocols is ETHERNET, USB, PCI-EXPRESS. SPI and I2C are used for short distance communication protocols SPI is a serial data communication protocol that provides high reliability, compactness and error free data transmission and reception. SPI has been developed by Motorola. The entire SPI communication is divided into master to slave and slave to master communication.SPI protocol is typically used for intra chip communication. In SPI both master and slave performs dual role of transmitter and receiver. The main advantage of SPI protocol speed is very high as compared to the other protocols like I2C. The high speed performance of SPI is possible because there is no need to transfer the slave address.SPI has been implemented by many companies with several advancement.SPI protocol is having simple architecture, high speed data transfer and cost effective implementation so it is widely used for connecting peripherals to the microprocessor or microcontroller.SPI protocol is having some disadvantages like it does not have any particular addressing scheme and it lags in offering any flow control. The Universal Verification Methodology (UVM) consists of set of base class and class library files used for the development of verification environment constructed and

© 2019, IJCSE All Rights Reserved

UVM is a reusable SystemVerilog based on Verification environment.

Objective of this work is:

- Design Serial Peripheral Interface (SPI) protocol using Verilog.

- Verification Using Universal Verification Methodology

- Constructing UVM Test bench Architecture using SystemVerilog and Object Oriented Programming (OOP).

- > Test cases generation for Functionality Verification

- Maximize Coverage

### II. SERIAL PERIPHERAL INTERFACE

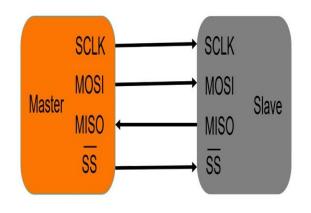

The Serial Peripheral Interface was developed by Motorola. SPI is a full duplex, synchronous and high speed bus communication protocol.SPI protocol used for short distance communication, primarily in embedded systems. Typical applications include sensors, Digital cards, Secure, and liquid crystal displays. Figure 1 shows the schematic diagram of SPI and SPI consists of four signals: serial clock (SCLK) output from master and slave select (SS\_bar)output from master master out slave in (MOSI) data output from master, master in slave out (MISO) data output from slave. SPI can operate with a single master device and more than one slave devices. The SPI operates in four different modes, based on the data transmitting and receiving on rising or falling edge of the serial clock [7].

**Figure 1: Serial Peripheral Interface**

- Master Out Slave In (MOSI) It is single bit signal generated by master based on internal shift in the shift register present in the master Device, It is single bit signal

- Master In Slave Out (MISO) It is single bit signal generated by slave during transfer of its shift register contents to the master device.

- Serial Clock (SCLK) This line is serial clock. This signal synchronizes the transmission.

- Slave Select (SS\_bar) This line is slave select line which is active low signal used by master device to select particular slave to start the communication.

### III. SPI DATA TRANSMISSION

Clock polarity and clock phase are the important parameters, used to define a clock format to be used by the SPI bus. Clock polarity is used to determine the idle state of the clock. If idle (or first) state is 0 so the polarity is 0 and idle (or first) state is 1 so the polarity is 1.

Modes in SPI :

The data exchange is defined by two parameters, one is clock polarity (CPOL), onther one is clock phase (CPHA).Figure-2 shows the timing diagram of SPI Modes it consists of four modes.

# Mode 0:

The data must be obtained before the rising edge of the first clock signal. The idle clock state is zero and MISO and MOSI lines data must be normal while the clock signal is high and can be changed when the clock signal is low. The data is captured on low to high clock transition and generated on high to low clock transition.

Figure 2: Timing diagram of SPI modes

# Mode 1:

The data must be obtained before the rising edge of the first clock signal. The idle clock state is zero and MISO and MOSI lines data must be normal while the clock signal is low and can be changed when the clock signal is high. The data is captured on high to low clock signal transition and generated on low to high clock signal transition.

Mode 2:

The data must be obtained before the falling edge of the first clock signal. The idle clock state is one and MISO and MOSI lines data must be normal while the clock signal is low and can be changed when the clock signal is high. The data is captured on high to low clock signal transition and generated on low to high clock transition.

Mode 3:

The data must be obtained before the falling edge of the first clock signal. The idle clock state is one and MISO and MOSI lines data must be normal while the clock is high and can be changed when the clock signal is low. The data is captured on low to high clock signal transition and generated on high to low clock signal transition.

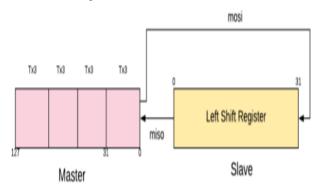

Figure 3: Shift Register

## International Journal of Computer Sciences and Engineering

Figure 3 shows the shift register and it is acts as a ring buffer. Both SPI master and slave have a shift register.when the master wants to send the data to the slaves, first it loads the data into its shift register and data sent from master most significant bit to slave receives register least significant bit.

## IV. UNIVERSAL VERIFICATION METHODOLOGY(UVM)

The Universal Verification Methodology (UVM) is a set of base class SystemVerilog based on Verification environment [3].

UVM consists of main three types of classes

- uvm\_object: It is a base class based operational methods; instance identification fields and random seeding were in it. All uvm\_component and uvm\_transaction derived from uvm\_object. uvm\_object methods are create, clone, copy, print, record etc.

- uvm\_transaction: It is used to generate stimulus and analysis. It is the root base class for uvm component.

- uvm\_component: Uvm Components are quasi static objects that exit throughout simulation.uvm components are UVM Top, Test, Environment, Agent, Sequence Item, Sequence, Driver, Sequencer, Monitor, and Scoreboard.

UVM provides the following different phases for all uvm components.

- Build\_phase: This phase creates and configures additional component hierarchies if required depending on configuration and factory settings.

- Connect\_phase: Connect ports of different UVM components to each other using TLM port and export.

- End\_of\_elaboration\_phase: This phase performs display environment print topology, open files and defines additional configuration settings for components.

- Start\_of\_simulation\_phase: This phase performs display environment print topology.

- Run\_phase: Components implement behaviour that is exhibited for the entire run-time, across the various run time backward compatibility with OVM.

- Extrat\_phase: Display final state information.

- Check\_phase: It Checks that no unaccounted for data remain.

- Report\_phase: This phase reports of all the simulation results.

- Final\_phase: Close files and terminate simulation.

# Vol. 7(14), May 2019, E-ISSN: 2347-2693

### **V. VERIFICATION ENVIRONMENT**

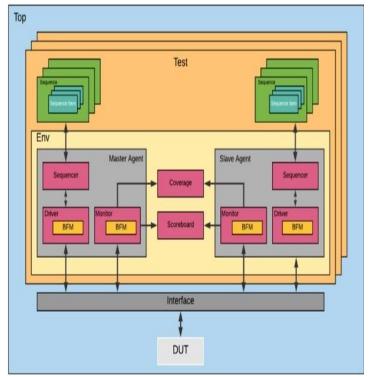

Figure 4: UVM verification environment

Figure 4 shows the UVM functional verification environment.

- > UVM Test bench Top: The test bench structure including the test class interfaces and DUT are instantiated in the top module.

- UVM Test: Using test case checks and verifies specific features of a design.

- UVM Environment: UVM environment contains multiple and reusable verification environment component and defines their default configuration as required by the application.

- UVM Agent: UVM agent contains monitor, driver and sequencer into a single entity by instantiating connecting the components together via TLM interfaces.

- UVM Sequence: UVM sequence is made up of several data items.

- UVM Driver: UVM driver is used to drive signals to interface of the design.

- UVM Sequencer: UVM sequencer generates data transactions as class objects and sends it to the driver.

- UVM Monitor: UVM Monitor is a responsible for capturing design interface signal activity and transfer to transaction level data objects.

- UVM Scoreboard: UVM scoreboard is a verification component it contains checkers and verifies the functionality of a design.

**VI. WISHBONE INTERFACE**

## Vol. 7(14), May 2019, E-ISSN: 2347-2693

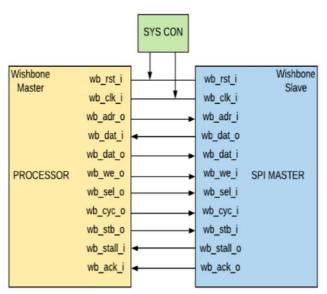

Figure 5: Wishbone Interface

The wishbone interface bus uses both master and slave interfaces. IP cores with master interface generate bus cycle transactions, IP core with slave interface receive the designed bus cycle transactions. Figure 5 shows the wishbone interface for portable and IP cores enables a design methodology for use with semiconductor IP cores. Master and slave IP cores communicate through an interconnection interface called SYSCON and it is a data flow interconnection, point to point interconnection, shared bus interconnection and crossbar interconnection [4].

# VII. SPI MASTER ARCHITECTURE

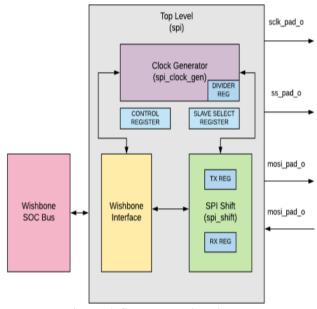

The SPI Master IP core design is suitable with the bus principle and SPI protocol. At the host side, the design is compatible with the slave devices of wishbone bus specification complaint. Figure 6 shows the SPI master architecture. The structure of the wishbone complaint SPI master core devices can be divided into three functional units: Serial interface, clock generator and wishbone interface. Clock generator is responsible for the clock signal generation from the external system clock. Shift register shift bit by bit and top module includes the clock generation, shift register and wishbone interface and also top modules includes the SPI signals and four internal signals. Serial data transfer module forms the data transfer core module and wishbone interface is a portable and flexible IP cores enables a design methodology for use with semiconductor IP cores [8].

**Figure 6: SPI Master Architecture**

VIII. RESULTS AND DISCUSSION

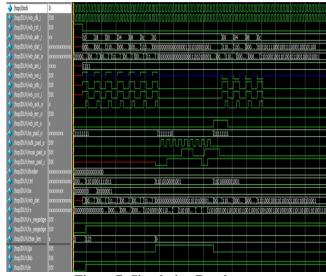

**Figure 7: Simulation Results**

Figure 7 shows the SPI Master core communication is synchronized sclk\_pad clock signal, which is synchronized to the wb\_clk base clock signal Before start the transfer, the master and slave configure its control register. Figure 8 shows the coverage results of SPI master core.

| Design Scope ◄                         | Hits<br>% ◄ | Coverage % |  |

|----------------------------------------|-------------|------------|--|

| spi_test_pkg_svh_unit                  | 100.00%     | 100.00%    |  |

| spi_LSB_wr_xtns/body/#ublk#98387108#46 | 100.00%     | 100.00%    |  |

| spi_LSB_rd_xtns/body/#ublk#98387108#46 | 100.00%     | 100.00%    |  |

| spi_vbase_seq/body                     | 100.00%     | 100.00%    |  |

| spi scoreboard                         | 100.00%     | 100.00%    |  |

| Total Coverage:    |        |        |          |        | 100.00% | 100.00%    |

|--------------------|--------|--------|----------|--------|---------|------------|

| Coverage<br>Type ◄ | Bins 4 | Hits 🖪 | Misses 🖪 | Weight | % Hit ◄ | Coverage ◄ |

| <u>Covergroups</u> | 17     | 17     | 0        | 1      | 100.00% | 100.00%    |

| Assertions         | 13     | 13     | 0        | 1      | 100.00% | 100.00%    |

Figure 8: Coverage Result for SPI Master Core

### IX. CONCLUSION AND FUTURE SCOPE

In this paper, a reusable SystemVerilog based UVM environment developed for SPI master core. The test bench enable to validate and verify the full duplex serial data transfer between the master agent and slave agent core devices for the various character length and data formats respectively and also done functional and code coverage. The verification result provides the details of the verification environment. In future SPI master controller can be extended to advanced WISHBONE B4 specification.

#### ACKNOWLEDGMENT

Centre of Excellence in VLSI design, Department of Electronics and Communication Engineering PESCE, Mandya and VLSIGuru Bangalore. First I would like to express my gratitude to my Guide Dr. Punith Kumar M B and also our HOD Dr. K.A.Radhakrishna Rao who gave me the opportunity to do this project on the topic Design and Verification of SPI master core using UVM, I would also like to thanks to my parents and friends.

### REFERENCES

- Zhili Zhou, Zheng Xie, Xin'an Wang and Teng Wang "Development of verification environment for SPI master interface using SystemVerilog" ICSP,2012 IEEE 11th international Conference.

- [2]. T.Liu and Y.Wang, "IP design of universal multiple devices SPI interface" in AntiConterfeiting, Security and identification (ASID), 2011 IEEE International Conference on IEEE,2011,pp. 169-172.

- [3]. W.Ni and J. Zhang, "Research of reusability based on UVM verification," in 2015 IEEE 11th International Conference on ASIC, Nov 2015, pp. 1-4.

## Vol. 7(14), May 2019, E-ISSN: 2347-2693

- [4]. A.K. Swain and K. Mahapatra, "Design and Verification of WISHBONE bus interface for System-on-Chip integration," in india Conference (IINDICON),2010 Annual IEEE .IEEE,2010,pp. 1-4.

- [5].K. Fathy and K. Salah, "An Efficient Scenario Based Testing Methodology Using UVM," in 2016 17th International Workshop on Microprocessor and SOC Test and Verification (MTV), Dec 2016, pp. 57–60.

- [6]. R.Prasad and C.S.Rani, "UART IP CORE VERIFICATION BY USING UVM," IRF International Conferences, 15 2016

- [7].K.Aditya, M.Sivakumar,F.Noorbasha, and P.B.Thummalakunta, "Design and Functional Verification of a SPI Master Slave Core Using System Verilog," International Journal of Computional Engineering Research,05 2018.

- [8]. S.Anantha , M.K.Kumar, and J.K. Bhandari, "Design and verification of SPI," International Journal of Engineering Development and Research(IJEDR), vol 1, pp. 130-136, Dec. 2014.

- [9]. Srot and Simon, SPI Master core Specification, 2004. [online]. Available: https://opencores.org/project/spi

- [10]. R.Herveille, SPI Core Specification, 2003.[online]. Available: https://opencores.org/project/simple\_spi

### **Authors Profile**

**Dr. Punith Kumar M B** was born in Mandya, India, in 1985. He received the B.E. Degree in Electronics and Communication Engineering from The National Institute of Engineering, Mysore in 2007, and the M.Tech in VLSI Design and Embedded Systems from PES College of Engineering, Mandya under the The Visvesvaraya Technological University (VTU), Belgaum in 2010 and Ph.D. degrees in Electronics from the University of Mysore (UoM), Mysore, India, in 2017.

In 2007, he joined the Department of Electronics and Communication Engineering as a Lecturer in JVIT, Bidadi, Bangalore. In 2010, he joined the Department of Electronics and Communication Engineering as a Assistant Professor in BGS Institute of Technology, BG Nagar, Mandya. In 2017, he joined the Department of Electronics and Communication Engineering as a Associate Professor in PES College of Engineering Mandya. His current research interests include image processing, video processing, video shot detection etc.

**Mr. Sreekantesha H N** was born in Hassan, India. Pursuing M.TECH (VLSI Design and Embedded System Design) from PESCE College of Engineering, Mandya, Karnataka. Completed BE in ECE from Government Engineering College, K R PET.